e-ISSN: 2582-5208 Technology and Science

International Research Journal of Modernization in Engineering Technology and ScienceVolume:03/Issue:05/May-2021Impact Factor- 5.354www.irjmets.com

# A DISTINCT APPROACH TO COMPUTER ARCHITECTURE

# Rohini Rathod<sup>\*1</sup>, Prakhar Pandey<sup>\*2</sup>, Aayush Tiwari<sup>\*3</sup>

\*1Professor, Department of Electronics Engineering, SLRTCE, Thane, Maharashtra, India \*2Student, Department of Electronics Engineering, SLRTCE, Thane, Maharashtra, India \*3Student, Department of Electronics Engineering, SLRTCE, Thane, Maharashtra, Indiat

# ABSTRACT

As of late, propels in PC engineering have eased back drastically with most recreation results exhibiting just steady design advancement. This is additionally exacerbated by the expanded processor and framework intricacy prodded by a limitless number of semiconductors available to PC planners. PC engineers produce a nearsighted perspective on their frameworks through the viewpoint of moderate, profoundly definite programming reenactment or quick, coarse-grained programming recreation, with constancy consistently being referred. By utilizing silicon innovation scaling in Field Programmable Gate Arrays (FPGAs), equipment can be utilized to speed up reenactment, copying, or prototyping of frameworks. Besides, on the grounds that the base parts are reconfigurable, a similar framework can be utilized for an assortment of examination projects, amortizing the expense, both in dollars and in learning time. In this paper, we present the third era of the Berkeley Emulation Engine or BEE3 framework. We show another coordinated effort technique among the scholarly world and industry and analyze the modern and scholastic framework configuration measure. The BEE3 is a creation multi-FPGA framework with up to 64 GB of DRAM and a few I/O subsystems that can be utilized to empower quicker, bigger and higher constancy PC engineering or different frameworks research. Utilizing a broadly accessible equipment stage additionally works with a product local area that can create and share programming modules, subsequently empowering quick framework advancement for PC engineering research.

Keywords: RAMP, COA, Operating System, BEE3, Design Mapping, FPGA.

## I. INTRODUCTION

Verifiably, programming reproduction has been the vehicle of decision for considering PC design due to its adaptability and minimal expense. Unfortunately, clients of programming test systems should pick between elite or high devotion copying. Interestingly, building equipment in Application Specific Integrated Circuits (ASICs) gives superior and precise outcomes, yet comes up short on the adaptability to investigate various plans. It is likewise over the top expensive. These tradeoffs have hindered our capacity to completely investigate and assess new PC models. This absence of recreation devotion and speed is additionally exasperated by the increment in multithreaded or potentially multicore chip designs.

Generally, PC draftsmen have utilized expanding semiconductor thickness to execute a solitary huge processor that endeavors guidance level parallelism (ILP). In any case, proceeded with execution gains from ILP are getting progressively hard to accomplish because of restricted parallelism among directions in commonplace applications [1]. Similarly, the issues related with planning ever-bigger and more unpredictable solid processor centers are getting progressively huge. These issues incorporate higher bug rates, longer plan and check times brought about by the plan intricacy, and the need to plan for expanding wire delay [2]. This reality has prodded incredible interest in abusing string level parallelism (TLP) among free strings to proceed with chronicled microchip execution patterns. These multithreaded structures successfully incorporate different homogeneous or heterogeneous processors onto a solitary chip.

Programming based test systems permit analysts to assess little benchmarks or pieces of bigger benchmarks utilizing guidance level recreation, however are too delayed to even consider mimicking whole applications in a sensible time. Confounded chip multiprocessor plans deteriorate this issue by necessitating that numerous processors be recreated at the same time. The intricacy of even the most fundamental multithreaded models limits guidance level reproduction to a successful "clock rate" of under 1 MHz; most test systems, particularly RTL ones, accomplish significantly less. Recreation speed hence restricts the degree and adequacy of exploration that can be acted in sensible measures of time, abridging huge development and encouraging future gradual examination. BEE3 utilizes best in class Xilinx Virtex 5 Field Programmable Gate Arrays (FPGAs) joined with extensive measures of DRAM on a solitary printed circuit board (PCB) to make an adaptable calculation texture that can execute billions of tasks each second. The subsequent stage executes code in any event two significant

## e-ISSN: 2582-5208

# International Research Journal of Modernization in Engineering Technology and ScienceVolume:03/Issue:05/May-2021Impact Factor- 5.354www.irjmets.com

degrees quicker than execution-driven programming recreation and a significant degree quicker than past equipment copying utilizing conventional varieties of FPGAs. Utilizing BEE3, specialists can quickly model an assortment of structures in a moderately short measure of time by utilizing a store of low-level segment plans. BEE3 permits nitty gritty examination of numerous subjects identified with processor and framework configuration, including memory progressions, TLP extraction techniques, TLP arranged programming plan for working frameworks and significant level applications, reconfigurable structures, installed frameworks, and ISA expansions. This stage can likewise be utilized as an application gas pedal for applications that guide well to the FPGA design.

## II. BEE3 OUTLINES

The BEE3 framework is made out of an equipment stage, related gateway (Verilog or VHDL code to program the FPGA), and the product stack as demonstrated in Figure 1. The BEE3 printed circuit board (PCB) can oblige three unique variations of the Xilinx FPGA Virtex 5 family: General rationale (LXT), signal handling (SXT), and implanted frameworks (FXT). The BEE3 framework is bundled in a 2U rack-mountable nook that has a few I/O subsystems that can be utilized to associate a few BEE3 frameworks together or couple the BEE3 to workers or different gadgets.

## Hardware Configuration of BEE3

The BEE3 machine consists of separate PCBs. If the reader is acquainted with the BEE2 machine, the manage FPGA has been removed, and a smaller PCB that gives FPGA programming, continual garage and console I/O capability has been added. The foremost BEE3 PCB has 4 Virtex five FPGAs, as much as sixty-four GB of DRAM, and numerous I/O ports.

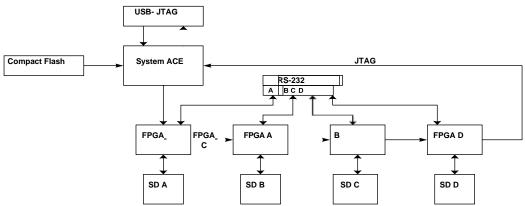

By transferring the manage capability off the principle PCB, the general layout complexity is decreased and layout flexibility is increased. This reduces PCB routing congestion and permits for very little manage common sense or a greater complicated manage and I/O interface tailor-made for a specific application. The manage and I/O PCB suits in a modular sub-chassis [2]. Figure 2 presents the block diagram illustrating the I/O PCB usefulness for FPGA programming, low transmission capacity I/O, and bit record (Compact Flash) and information (SD Flash) stockpiling.

The control PCB utilizes a Xilinx System ACE chip to deal with a Compact Flash card and program the FPGAs. Various digit document variants can be put away in the Compact Flash card and the System ACE can choose which form to use to program the FPGAs. The Xilinx JTAG case is contained in the sub-undercarriage also. Therefore, just a USB link combined with the programming on a PC have is required. There are four SD Flash openings (one for every FPGA) that give determined capacity to each FPGA utilizing a SPI interface. Similarly, one RS-232 actual association for each FPGA is accessible for a support interface. The primary BEE3 PCB has two 50-pin headers that give these interfaces: One header for the JTAG and framework control and the other header for the SD SPI and RS-232 interfaces. Accordingly, other control and I/O PCBs can be made and modified for a specific application space.

A BEE3 framework could be worked as a heterogeneous or homogeneous FPGA stage, utilizing FPGA-explicit highlights at the granularity needed by the framework.

The CX4, PCI-E, or 1 GbE interfaces give an assortment of approaches to interconnect numerous BEE3 frameworks or supplement workers with particular equipment for application speed increase. Utilizing

### e-ISSN: 2582-5208 International Research Journal of Modernization in Engineering Technology and Science **Impact Factor- 5.354** www.irjmets.com

moderate execution gauges, Table 1 gives least transmission capacity appraisals to the I/O interfaces. The DDR2, ring, and QSH interfaces work at 250 MHz, DDR. Both the DRAM and ring interfaces have two channels and move 8 bytes for each clock. Interestingly, the QSH is a solitary channel that can move just 4 bytes all at once.

### **Software Configuration**

Volume:03/Issue:05/May-2021

There are a few layers that make up the product framework. The gateware depicts the product needed to program the FPGAs to design them for a specific errand. A portion of the gateware is given by Xilinx, while other gateware segments are given by the local area. The BEE3 framework incorporates a reference plan that practices a large portion of the frameworks usefulness. Besides, the force on test suite tests all the subcomponents to ensure usefulness. The DDR2 interface is likewise accessible online.

The Xilinx gateware is related with large numbers of the hard macros and gives basic models that should be redone to really be helpful. Xilinx gives an assortment of gateware, some of which like the PCI-Express, 10 Gb XAUI interface, and 1 Gb Ethernet MAC macros can be adjusted for use with the BEE3. The client or an outsider is needed to redo these underlying plans for any application necessitating that usefulness. Xilinx likewise gives other valuable gateware parts, for example, the 32-bit Microblaze processor. The most recent variant of the Microblaze consolidates a MMU, permitting full forms of working frameworks to be run. Lamentably, the Microblaze is conveyed as a "black box", without source code, so it can't be redone.

#### III. **DESIGN MAPPING**

The BEE3 is a reconfigurable framework that can be reconstructed for use across numerous applications and exploration fields. Here we present a couple of uses from the RAMP people group utilizing the past BEE2 framework. Then, we present a few instances of utilizing BEE3 in different areas. At last, we give setting to utilizing BEE3 in PC design research.

## **The Shades of Ramp Colors**

The RAMP consortium has fostered a few working models zeroing in on multiprocessor frameworks. "Slope Blue", created at UC Berkeley, has fabricated a 1000+ center framework utilizing 21 BEE2 frameworks running MicroBlaze processors at 90 MHz [29]. This enormous scope framework is extremely encouraging in light of the fact that it exhibits that huge scope FPGA-based frameworks can be fostered that run at sensible equipment speeds. "Incline Red", created at Stanford University, is an eight-center conditional memory framework on a solitary BEE2 board. It gives a product advancement climate to conditional memory programming. The equipment isn't cycle precise, however runs at 100 MHz and gives programming execution results two significant degrees quicker than the product just recreation [30]. "Slope White", created at UT Austin, parts the product test system into two segments, one running in equipment and the other running in programming [31]. Moreover, a gathering at CMU utilizes a comparable novel reenactment approach, exhibiting reproduction accelerate of one to two significant degrees for a recreation framework made out of 16 processors.

## Utilizing BEE3 in an alternate exploration space

Boolean Satisfiability (SAT) solvers are broadly utilized as the basic thinking motor for electronic plan computerization, just as in numerous different fields like man-made reasoning, hypothesis demonstrating, and program confirmation. Thus, if huge advances happen in this one territory, numerous different fields profit by this by empowering bigger issue sizes as well as quicker calculation. In [1], Davis have planned the SAT issue onto a BEE3 framework coupled to a host PC, utilizing the FPGA as a co-processor. The way in to this co-processor engineering is the novel way to deal with change Boolean rationale into a minimal programmable construction to exploit the FPGA's high data transfer capacity and low idleness on-chip block RAM. By parting the SAT issue into an equipment helped programming arrangement, the creators had the option to give programming adaptability and equipment speed increase all the while. Different areas, for example, DSP-based oil and gas investigation information preparing and monetary estimations are likewise managable to FGPA speed increase

## **Utilizing the BEE3 for Computer Architecture Research**

Since the BEE3 is accessible and underway, we have begun to really utilize it in our exploration. In spite of the fact that it is untimely to report results, since we are still intensely engaged with gateware foundation assembling, this segment portrays a couple of the undertakings we have started. We additionally attempt to feature the qualities and shortcoming of the BEE3 framework.

## e-ISSN: 2582-5208

# International Research Journal of Modernization in Engineering Technology and ScienceVolume:03/Issue:05/May-2021Impact Factor- 5.354www.irjmets.com

The essential benefit of a copying stage like the BEE3 for engineering research is that it is feasible to run genuine jobs at sensible speed in a very much instrumented climate. The plans delivered in a FPGA are not serious in clock speed with "genuine" executions, being 10-20X slower. Be that as it may, this is still quick enough to run genuine applications to culmination, instead of microbenchmarks or application bits. Planning a processor center with a clock pace of 100 MHz is clear, and a few such centers fit on a solitary FPGA. This working recurrence is a couple of times more slow than late scholarly ASIC processor plans. Similarly, extra rationale might be added to a plan to assemble and log any data required in an examination. Extra rationale may likewise be added to "twist" time to deliver cycle-precise imitations when required. We are beginning to explore different avenues regarding the plan of a message passing framework that is presented to the ISA of a customary processor, as an option in contrast to the utilization of conveyed shared memory in a many-center setting. When all is said in done, BEE3 gives a stage to numerous and multicore research that centers around utilizing straightforward base processors.

## IV. RESULTS AND DISCUSSION

Truly, equipment copying stages utilizing varieties of FPGAs have been utilized to produce quick prototyping frameworks that can reproduce whole applications at a RTL level. Sadly, endeavors to incorporate multiprocessor plans to these frameworks have been restricted by poor FPGA rationale usage, restricted interconnectivity in the FPGA clusters, and helpless word-size information control by cycle width FPGA rationale units. Moreover, crossing chip limits has been a central constraint on the grounds that off-chip transfer speed is considerably less than on-chip transmission capacity. Be that as it may, as silicon innovation has improved, the limit of reconfigurable gadgets and per-pin transfer speed has drastically improved. Today, various straightforward processors can be planned to a solitary FPGA and by and large, FPGA limit and expanded per-pin data transmission empower a lot more noteworthy prototyping adaptability.

One of the primary remarkable FPGA-based equipment emulators was the Rapid Prototyping motor for Multiprocessors (RPM). This underlying equipment emulator for multiprocessor models moved past just noticing framework conduct like transport traffic. RPM was worked to model Multiple Instruction Multiple Data (MIMDs) multiprocessor machines. The configurable innovation accessible for this undertaking empowered reconfigurable memory framework executions with a fixed SPARC processor. Every processor module was executed on a solitary PCB with up to eight loads up associated with a backplane and host machine. RPM zeroed in on the memory arrangement of enormous multiprocessor frameworks. Despite the fact that RPM consolidated SPARC processors with FPGAs, RPM protected the memory framework straightforwardness as far as possible up to the processor. Lamentably, RPM came up short on the product framework to make it simple to utilize and thus, it neglected to accomplish inescapable selection like programming test systems.

After 10 years, The Flexible Architecture for Simulation and Testing (FAST) was created to research TLP models. Like RPM, this framework had full memory framework straightforwardness up to the processor. Quick utilized straightforward processors (MIPS R3000 and R3010) joined with cutting edge FPGAs and memory chips on a solitary PCB to make an adaptable register texture that can execute a huge number of guidelines each second. The subsequent climate executes code in any event two significant degrees quicker than execution-driven programming recreation and a significant degree quicker than past equipment imitating utilizing nonexclusive varieties of FPGAs. Quick was planned unequivocally to empower memory framework and extra engineering examination, for example, theoretical coprocessors for Thread Level Speculation or other off-load motors, in enormous multiprocessor (MP) or little, quick CMP frameworks. Quick had the option to reproduce the memory inactivity for both MP and CMP frameworks, just as anyplace in the middle by falsely choking the fast SRAM. The FAST framework was versatile up to 16 PCBs, empowering up to 64 processor frameworks, albeit only one framework was at any point fabricated. Like RPM, FAST likewise endured due to an absence of assets and coming about programming framework.

The BEE3 is an illustration of another kind of firmly coupled modern and scholarly joint effort. For this situation, we have fostered a framework dependent on scholastic determinations and that is accessible to both scholarly community and industry. This is a sensational change from giving exploration subsidizing to a specific task or giving enhancement project support, e.g., silicon chip back-end measure and additionally manufacture support, and has numerous advantages over the ordinary government or modern financing process. This coordinated effort model likewise has it challenges. Not all undertakings are managable to industry advancement. There might be issues identified with protected innovation and authorizing. Highlight creep and detail deviation may likewise

e-ISSN: 2582-5208

# International Research Journal of Modernization in Engineering Technology and ScienceVolume:03/Issue:05/May-2021Impact Factor- 5.354www.irjmets.com

be an issue for projects that have long time skylines bringing about something that neither industry nor the scholarly world need. For this situation, we had the option to work intently and successfully with the scholarly world and other industry accomplices and this assisted with ensuring an entirely good result. The BEE3 additionally profits by an outsider conveyance component that might be hard to replicate. At last, it could be hard to characterize a task all around ok from its beginning that industry can give an elective component.

# V. CONCLUSION

The underlying raise and testing of the BEE3 framework has been fruitful. We have tried the entirety of the subsystems at or above target working recurrence and have discovered no issues. The total creation BEE3 framework in its 2U skeleton is appeared in Figure.

The conveyance of the primary creation run of authorized BEE3 framework occurred in August 2008. The BEE3 framework was finished quicker and better than past scholastic planned multi-FPGA frameworks. The outcome is a framework with better sign trustworthiness and less expensive PCB producing costs. Like all past multi-FPGA PCBs, the BEE3 framework is not even close to the underlying \$5,000 target PCB cost, regardless of whether all the PCB parts were free. It is likewise the situation that the BEE3 won't supplant programming reenactment in PC design, yet expand the examination cycle with equipment either as a reproduction gas pedal, programming advancement stage, or a prototyping stage. This is a reasonable technique to once again introduce equipment back into the examination cycle for a more extensive class of structures and frameworks research. At long last, we have introduced a short overview of RAMP projects that exhibit the devotion range and assortment of use models for frameworks like BEE3. Contingent upon the objective, BEE3 can give a wide scope of loyalty without the presentation sway that product recreation displays. BEE3 won't displace programming test systems, at the same time, with some product foundation building, BEE3 gives an answer as a PC design research stage for multicores and numerous centers. We have shown this by building the Beehive many-center system. Outside of our examination bunch, the fundamental introductory objective for the BEE3 is the RAMP consortium. This assortment of colleges has numerous progressing projects and our expectation is that an energetic local area proceeds to create and share framework to empower examination and joint effort across college limits. These examination regions will be sped up by a local area sharing and supporting a typical stage.

## VI. REFERENCES

- [1] D.W. Wall, "Limits of Instruction-Level Parallelism," WRL Research Report 93/6, Digital Western Research

- [2] John D. Davis, Charles P. Thacker, Cheng Chang, "BEE3: Revitalizing Computer Architecture Research", MSR Technical Report MSR-TR-2009-45

- [3] J. H. Ahn, W. J. Dally, et al., "Evaluating the Imagine Stream Architecture," Proceedings of the 31st Annual International Symposium on Computer Architecture, Munich, Germany, June 2004

- [4] http://repository.eecs.berkeley.edu/

- [5] <u>http://www.xilinx.com/support/documentation/virtex-5\_data\_sheets.htm</u>

- [6] <u>https://www.informationweek.com/architecture/bee3-microsoft-fpgas-and-the-future-of-computer-architectures/d/d-id/1065476</u>